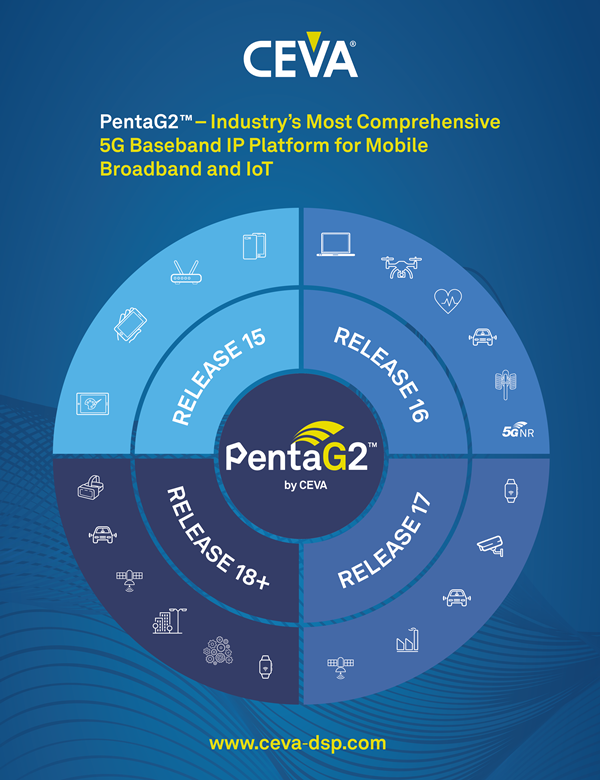

[smartPC사랑=남지율 기자] CEVA가 자사의 2세대 5G 플랫폼 아키텍처인 PentaG2을 발표했다. PentaG2는 최적의 신호 체인 프로세싱(signal chain processing)을 위해 고성능 디지털 신호 프로세서(DSP)와 특수 목적의 가속기를 결합한 포괄적인 하드웨어/소프트웨어 IP 플랫폼이다. 이전 모델에 비해 4배 향상된 전력 효율성을 자랑하며, 모바일 광대역과 사물인터넷(IoT)을 위한 새로운 모델의 확산을 가속화하고 5G 모뎀 설계를 내장하고자 하는 핸드셋 기기 OEM 업체의 진입장벽을 낮추는 것을 목표로 한다.

최근 발표된 에릭슨 모빌리티 보고서에 따르면 셀룰러 IoT 연결이 2021년 기준 19억개인 반면, 오는 2027년에는 전체 89억개 중 55억개를 차지할 것으로 예상했다. 뿐만 아니라 고정 무선 접속(FWA) 연결의 경우 2021년 9,000만 개에서 2027년에는 약 2억 3,000만개에 이를 것으로 전망했다. PentaG2는 완전한 LTE/5G 모뎀 설계에 필요한 핵심 구성요소를 갖춘 종합 플랫폼을 제공한다.

따라서 모바일 광대역과 IoT 분야에서 이러한 시장 기회를 활용하거나 5G 핸드셋 시스템온칩(SoC)을 자체적으로 개발하고자 하는 반도체 회사와 OEM 업체의 진입장벽을 낮춰준다.

PentaG2 플랫폼의 구성은 다음과 같다.

- PentaG2-Max는 핸드셋과 CPE/FWA 터미널, 밀리미터파(mmWave), NR-사이드링크(NR-Sidelink) 및 셀룰러 V2X(C-V2X)의 eMBB(enhanced Mobile BroadBand), AR/VR을 지원하는 초고신뢰저지연 통신(URLLC) 유즈 케이스를 대상으로 한다. 광범위한 워크로드를 효율적으로 처리하는 세계 유일의 완전한 IP 오퍼링(IP offering)으로, Sub-6와 밀리미터파 5G 광대역 모두에서 5G 고급화를 기대하는 3GPP(3rd Generation Partnership Project) 릴리즈 16과 17을 필요로 하며, 이로 인해 데이터 경로 처리 성능과 영역이 4배 향상된다.

– PentaG2-Lite는 LTE Cat1과 향후 3GPP 릴리즈17 및18 NR RedCap(Reduced Capacity, 일명 NR-Lite)을 포함한 다양한 저감 대역 유즈 케이스를 지원한다. 전력 소모를 최소화하기 위해 소형의 DSP 컨트롤러를 사용하고, 완전한 프로세싱 체인을 하드웨어 가속기로 구현하여 매우 효율적으로 기저 대역(Baseband)을 실행한다.

두 가지의 구성 모두 표준 인터페이스를 통해 채널 추정(Channel Estimation) 또는 고급 이퀄라이제이션(equalization)과 같이 고객이 보유한 자체 알고리즘 및 IP를 PentaG2 플랫폼과 결합할 수 있는 유연성을 제공한다.

CEVA 모바일 광대역 사업부 부사장 겸 제너럴 매니저인 가이 케셰트(Guy Keshet)는 "오늘날의 5G는 주로 스마트폰에 활용되고 있는 반면, 산업용과 로봇, 웨어러블, 헬스케어, 오토모티브, FWA 및 스마트 그리드 등의 시장에서는 5G의 잠재력을 완전히 활용하지 못하고 있다. PentaG2는 이러한 목적으로 자체적인 5G 모뎀을 개발하고자 하는 핸드셋 OEM 업체에게 완전한 베이스밴드 프로세싱 플랫폼(Baseband processing platform)을 제공하는 비용 및 전력 효율적인 솔루션이다"라고 말했다.

PentaG2 플랫폼 아키텍처는 현재까지 수백만대의 5G NR 스마트폰과 모바일 광대역 장치를 출하한 1세대 플랫폼의 성공적인 성과를 기반으로 설계되었다. 완전한 프로그래밍이 가능한 가속기와 코프로세서(coprocessor) 세트를 포함하고 있어 엔드 투 엔드(end-to-end) 인라인 신호 프로세싱 체인을 구성한다.

다음은 이번 PentaG2 플랫폼에 처음으로 도입된 가속기이다.

· 전체 Rx 비트 및 LLR 처리를 지원하는 비트 복조 장치(Bit Demodulation Unit)

· 전체 Tx 비트 처리를 위한 비트 변조 장치(Bit Modulation Unit)

· 이퀄라이저(Equalizer) 및 MAC 엔진 코프로세서 장치

· 5G LDPC(Low Density Parity Check) 인코더 및 디코더

· 5G 폴라(Polar) 인코더 및 디코더

다른 하드웨어 가속기에는 하이브리드 자동 재송 요구(HARQ, Hybrid Automatic Request), MLD(Maximum Likelihood Detection), 멀티 래딕스 DFT, 터보 FEC(Forward error correction), 비터비(Viterbi) FEC와 5G 링크 적응(link adaptation)을 위한 인공지능 신경망 코프로세서가 포함되며, 모든 가속기에는 용이한 통합을 위해 표준 AXI인터페이스가 함께 제공된다.

또한, 플랫폼에는 PHY(Physical Layer) 컨트롤, 하드웨어 가속 스케줄링(hardware acceleration scheduling) 및 통신 규약 스택(Protocol Stack) 실행을 위한 스칼라(scalar) DSP도 포함된다. 그리고 PentaG2-Max는 채널 추정(Channel Estimation)에 필요한 워크로드를 처리하기 위해 5G ISA 확장 기능을 갖춘 벡터 DSP도 갖추고 있다.

PentaG2 플랫폼은PDSCH(Physical Downlink Shared Channel), PUSCH(Physical Uplink Shared Channel), PDCCH(Physical Downlink Control Channel) 및 PUCCH(Physical Uplink Control Channel)를 포함한 플랫폼의 모든 하드웨어 가속기를 활용하고 컨트롤 DSP에서 실행되는 모든 5G 프로세싱 체인에 대한 완전한 L1 소프트웨어를 제공한다.

또한 PentaG2플랫폼에는 시스템 엔지니어, 설계자, 소프트웨어 개발자가 프리실리콘(Pre-Silicon) 및 설계를 모델링, 프로파일링, 디버깅할 수 있는 고급 플랫폼 System-C 시뮬레이션 환경이 포함되어 있다. 이는 개발을 더욱 단순화하고 가속화하는데 도움을 주며, 시뮬레이터는 알고리즘 개발을 위해 모든 PentaG2 구성요소와 인터페이스를 매트랩(MATLAB)과 함께 완벽히 지원한다. 그리고 모든 PentaG2 시스템은 FPGA 플랫폼의 에뮬레이션 환경을 이용하여 검증 가능하다.

PentaG2는 현재 선두업체 대상으로 라이선스 사용이 가능하며, 오는 하반기에는 일반 기업도 라이선스 사용이 가능할 예정이다. PentaG2 고객은 CEVA의 SoC 설계 서비스를 통해 시스템 설계와 모뎀 개발을 통합하고 지원하는 데에 도움을 받을 수 있다.

저작권자 © 디지털포스트(PC사랑) 무단전재 및 재배포 금지